# Programming Models for Many-Core Architectures

A Co-design Approach

Jochem H. Rutgers

#### Members of the graduation committee:

Prof. dr. ir. M. J. G. Bekooij University of Twente (promotor)

Prof. dr. ir. G. J. M. Smit University of Twente (promotor)

Prof. dr. J. C. van de Pol Dr. ir. J. F. Broenink Prof. dr. H. Corporaal University of Twente

Eindhoven University of Technology

Prof. dr. ir. K. L. M. Bertels Delft University of Technology

Prof. dr. ir. D. Stroobandt Ghent University

Prof. dr. P. M. G. Apers University of Twente (chairman and secretary)

### UNIVERSITY OF TWENTE.

Faculty of Electrical Engineering, Mathematics and Computer Science, Computer Architecture for Embedded Systems (CAES) group

CTIT Ph.D. Thesis Series No. 14-292 Centre for Telematics and Information Technology PO Box 217, 7500 AE Enschede, The Netherlands

This research has been conducted within the Netherlands Streaming (NEST) project (project number 10346). This research is supported by the Dutch Technology Foundation STW, which is part of the Netherlands Organisation for Scientific Research (NWO) and partly funded by the Ministry of Economic Affairs.

Copyright © 2014 Jochem H. Rutgers, Enschede, The Netherlands. This work is licensed under the Creative Commons Attribution-NonCommercial 4.0 International License. To view a copy of this license, visit http://creativecommons.org/licenses/by-nc/4.0/deed.en\_US.

This thesis was typeset using  $\LaTeX$ , TikZ, and Vim. This thesis was printed by Gildeprint Drukkerijen, The Netherlands.

ISBN 978-90-365-3611-0

ISSN 1381-3617; CTIT Ph.D. Thesis Series No. 14-292

DOI 10.3990/1.9789036536110

# Programming Models for Many-Core Architectures

#### A Co-design Approach

#### PROEFSCHRIFT

ter verkrijging van de graad van doctor aan de Universiteit Twente, op gezag van de rector magnificus, prof. dr. H. Brinksma, volgens besluit van het College voor Promoties in het openbaar te verdedigen op woensdag 14 mei 2014 om 14.45 uur

door

Jochem Hendrik Rutgers

geboren op 18 april 1984 te Winterswijk

### Dit proefschrift is goedgekeurd door:

Prof. dr. ir. M. J. G. Bekooij (promotor) Prof. dr. ir. G. J. M. Smit (promotor)

Copyright © 2014 Jochem H. Rutgers ISBN 978-90-365-3611-0

## **ABSTRACT**

It is unlikely that general-purpose single-core performance will improve much in the coming years. The clock speed is limited by physical constraints, and recent architectural improvements are not as beneficial for performance as those were several years ago. However, the transistor count and density per chip still increase, as feature sizes reduce, and material and processing techniques improve. Given a limited single-core performance, but plenty of transistors, the logical next step is towards *many-core*.

A many-core processor contains at least tens of cores and usually distributed memory, which are connected (but physically separated) by an interconnect that has a communication latency of multiple clock cycles. In contrast to a multicore system, which only has a few tightly coupled cores sharing a single bus and memory, several complex problems arise. Notably, many cores require many parallel tasks to fully utilize the cores, and communication happens in a distributed and decentralized way. Therefore, programming such a processor requires the application to exhibit concurrency. Moreover, a concurrent application has to deal with memory state changes with an observable (non-deterministic) intermediate state, whereas single-core applications observe all state changes to happen atomically. The complexity introduced by these problems makes programming a many-core system with a single-core-based programming approach notoriously hard.

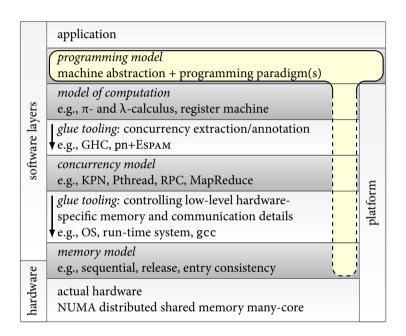

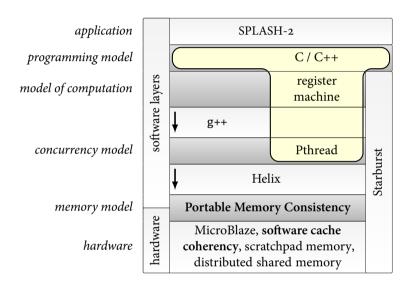

The central concept of this thesis is that abstractions, which are related to (many-core) programming, are structured in a single platform model. A platform is a layered view of the hardware, a memory model, a concurrency model, a model of computation, and compile-time and run-time tooling. Then, a *programming model* is a specific view on this platform, which is used by a programmer.

In this view, some details can be hidden from the programmer's perspective, some details cannot. For example, an operating system presents an infinite number of parallel virtual execution units to the application—details regarding scheduling and context switching of processes on one core are hidden from the programmer. On the other hand, a programmer usually has to take full control over separation, distribution, and balancing of workload among different worker threads. To what extent a programmer can rely on automated control over low-level platform-specific details is part of the programming model. This thesis presents modifications to different abstraction layers of a many-core architecture, in order to make the system as a whole more efficient, and to reduce the complexity that is exposed to the programmer via the programming model.

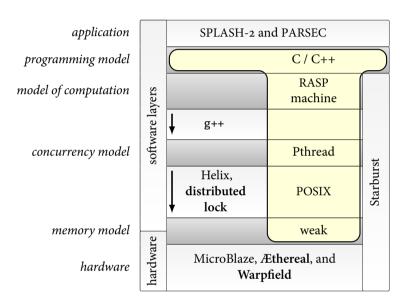

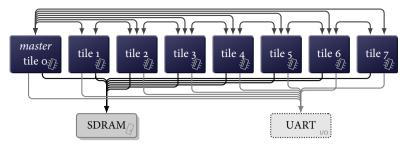

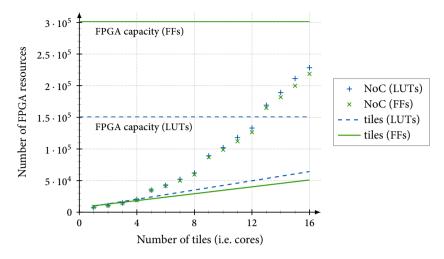

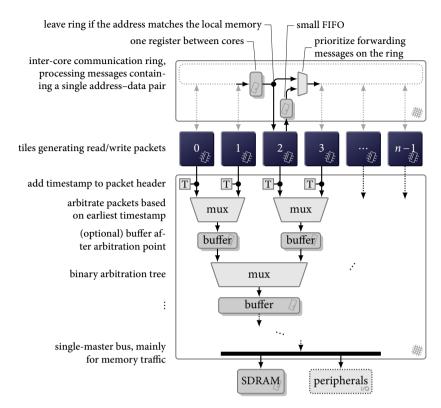

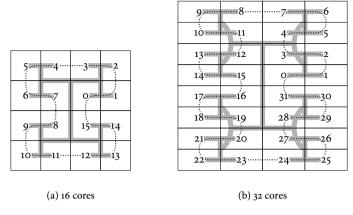

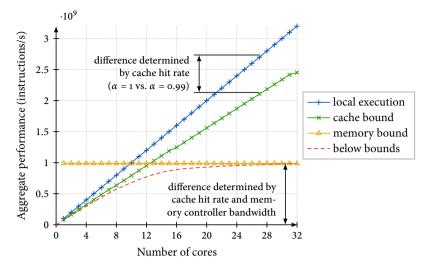

For evaluation of many-core hardware and corresponding (concurrent) programming techniques, a 32-core MicroBlaze system, named Starburst, is designed and implemented on FPGA. On the hardware architecture level, a network-on-chip is presented that is tailored towards a typical many-core application communication pattern. All cores can access a shared memory, but as this memory becomes a bottleneck, inter-core communication bypasses memory by means of message passing between cores and scratchpad memories. Using message passing and local memories, a new distributed lock algorithm is presented to implement mutexes. The network scales linearly in hardware costs to the number of cores, and the performance of the system scales close to linear (until bounded by memory bandwidth).

Different many-core architectures implement different memory models. However, they have in common that atomicity of state changes should be avoided to reduce hardware complexity. This typically results in a (weak) memory model that does not require caches to be coherent, and processes that disagree on the order of write operations. Moreover, porting applications between hardware with a different memory model requires intrusive modifications, which is error-prone work. In this thesis, a memory model abstraction is defined, which hides the memory model of the hardware from the programmer, and reduces hardware complexity by reducing the atomicity requirements to a minimum, but still allows an efficient implementation for multiple memory hierarchies. Experiments with Starburst demonstrate that software cache coherency can transparently be applied to applications that use this memory model abstraction.

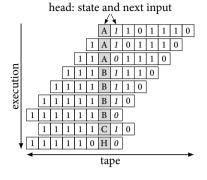

A common approach to exploit the parallel power of a many-core architecture is to use the threaded concurrency model. However, this approach is based on a sequential model of computation, namely a register machine, which does not allow concurrency easily. In order to hide concurrency from the programmer, a change in the model of computation is required. This thesis shows that a programming model based on  $\lambda$ -calculus instead is able to hide the underlying concurrency and memory model. Moreover, the implementation is able to cope with higher interconnect latencies, software cache coherency, and the lack of atomicity of state changes of memory, which is demonstrated using Starburst. Therefore, this approach matches the trends in scalable many-core architectures.

The changes to the abstraction layers and models above have influence on other abstractions in the platform, and especially the programming model. To improve the overall system and its programmability, the changes that seem to improve one layer should fit the properties and goals of other layers. Therefore, this thesis applies co-design on all models. Notably, co-design of the memory model, concurrency model, and model of computation is required for a scalable implementation of  $\lambda$ -calculus. Moreover, only the combination of requirements of the many-core hardware from one side and the concurrency model from the other leads to the memory model abstraction above. Hence, this thesis shows that to cope with the current trends in many-core architectures from a programming perspective, it is essential and feasible to inspect and adapt all abstractions collectively.

# SAMENVATTING

Het is onwaarschijnlijk dat de komende tijd de rekenkracht van een single-coreprocessor veel zal verbeteren. De kloksnelheid is beperkt door natuurkundige limieten en recente verbeteringen aan het ontwerp geven niet een snelheidswinst zoals die van enkele jaren geleden gaven. Toch nemen het aantal transistors per chip en de dichtheid nog steeds toe, omdat de gebruikte materialen en de productietechnieken blijven verbeteren. De combinatie van de beperkte rekenkracht van een enkele core en een overvloed aan transistors zal logischerwijs leiden tot *many-core-*processoren.

Een many-coreprocessor bevat minstens tientallen cores en meestal gedistribueerd geheugen, die zijn verbonden (maar fysiek gescheiden) door een netwerk waarin communicatie meerdere klokcycli in beslag neemt. Ten opzichte van een multicoreprocessor, waarin slechts enkele met elkaar verweven cores zitten en één bus en geheugen delen, worden een aantal complexe problemen zichtbaar. Het hebben van veel cores vraagt om veel parallelle taken om alle cores te benutten. Daarbij is communicatie gedistribueerd en decentraal geregeld. Om een dergelijke processor te kunnen programmeren moet de applicatie daarom ontworpen zijn voor parallellisme. Daarnaast moet deze applicatie kunnen omgaan met toestandsveranderingen van geheugen, waarbij de toestandsovergang non-deterministisch is, in tegenstelling tot sequentiële applicaties waarvoor toestandsveranderingen atomair lijken. De complexiteit als gevolg van deze problemen maakt het programmeren van een many-coresysteem met single-coreprogrammeertechnieken zeer moeilijk.

Het centrale concept van dit proefschrift is dat abstracties die gerelateerd zijn aan (parallel) programmeren, zijn gestructureerd in één platformmodel. Een platform is een gelaagde weergave van de hardware, het geheugenmodel, concurrencymodel, berekeningsmodel en de software voor compilatie en executie. Het *programmeermodel* is een specifiek perspectief op dit platform voor de programmeur.

Dit perspectief kan bepaalde details voor de programmeur verbergen of benadrukken. Een besturingssysteem biedt bijvoorbeeld een oneindig aantal virtuele processoren aan een applicatie—hoe de rekentijd van een processor wordt verdeeld over de processen wordt verborgen voor de programmeur. Echter, een programmeur wordt wel geacht exact aan te geven hoe rekenwerk moet worden opgesplitst en verdeeld over verschillende processen. Het programmeermodel geeft aan in hoeverre een programmeur kan vertrouwen op correcte aansturing van platformspecifieke details. Dit proefschrift beschrijft aanpassingen aan de verschillende abstractielagen, die het systeem als geheel efficiënter maken en de complexiteit reduceren waar de programmeur via het programmeermodel aan wordt blootgesteld.

Voor evaluatie van parallelle hardware en bijbehorende programmeertechnieken is er een 32-core MicroBlaze-systeem voor FPGA ontwikkeld, genaamd Starburst. Het bevat een netwerk dat is toegespitst op gangbare communicatiepatronen van many-coreapplicaties. De cores delen een geheugen. Echter, cores kunnen dit geheugen omzeilen door berichten uit te wisselen via kleine, lokale geheugens als bandbreedte naar het gedeelde geheugen een knelpunt wordt. Op basis van deze berichten tussen cores, is een gedistribueerd mutex-algoritme ontworpen. De hardwarekosten van het netwerk schalen lineair mee met het aantal cores. De totale rekenkracht van het systeem schaalt bijna lineair (totdat de geheugenbandbreedte verzadigd raakt).

Verschillende many-corearchitecturen ondersteunen verschillende geheugenmodellen. Deze hebben als overeenkomst dat atomaire toestandsveranderingen vermeden worden om de hardware eenvoudiger te maken. Het resulterende (zwakke) geheugenmodel vereist doorgaans niet dat caches coherent zijn, noch dat alle processen schrijfoperaties naar geheugen in dezelfde volgorde zien. Daarnaast vraagt het omschrijven van applicaties voor hardware met een ander geheugenmodel om ingrijpende aanpassingen. Dit is foutgevoelig werk. In dit proefschrift wordt een geheugenmodelabstractie gedefinieerd. Deze verbergt het geheugenmodel van de hardware voor de programmeur en versimpelt de hardware-implementatie, doordat de eisen aan de atomiciteit van toestandsveranderingen zijn versoepeld. Toch kan de abstractie efficiënt worden geïmplementeerd op verschillende geheugenarchitecturen. Experimenten met Starburst laten zien dat software cache coherency automatisch kan worden toegepast op applicaties die deze abstractie gebruiken.

Doorgaans wordt het threadingmodel gebruikt om parallellisme van de hardware te benutten. Echter, dit model is gebaseerd op een sequentieel berekeningsmodel, namelijk een registermachine, die concurrency niet eenvoudig toelaat. Een ander berekeningsmodel is nodig om concurrency voor de programmeur te verbergen. Dit proefschrift laat zien dat een op  $\lambda$ -calculus gebaseerd programmeermodel het onderliggende concurrency- en geheugenmodel wel kan verbergen. Tevens kan de implementatie voor Starburst omgaan met trage netwerkcommunicatie, software cache coherency en niet-atomaire toestandsveranderingen. Deze aanpak past daarom goed bij de trends in schaalbare many-corearchitecturen.

Aanpassingen in de abstractielagen en bovengenoemde modellen hebben invloed op andere abstracties in het platform, maar voornamelijk op het programmeermodel. Om het systeem als geheel en de programmeerbaarheid te verbeteren moeten verbeteringen in de ene abstractielaag passen bij de eigenschappen van andere lagen. Daarom wordt in dit proefschrift co-design toegepast op alle modellen. Co-design van het geheugenmodel, concurrencymodel en berekeningsmodel is bijvoorbeeld noodzakelijk voor een schaalbare implementatie van  $\lambda$ -calculus. Daarnaast leidt alleen de combinatie van eisen van many-corehardware van de ene kant en het concurrencymodel van de andere kant tot de genoemde geheugenmodelabstractie. Dit proefschrift laat dus zien dat het essentieel en haalbaar is om alle abstracties gezamenlijk te beschouwen en aan te passen, om vanuit een programmeerperspectief om te kunnen gaan met de huidige trends in many-corearchitecturen.

# Dankwoord

Eén woord per acht minuten. Als je dat gedurende het promotietraject toevoegt aan je proefschrift, dan heb je aan het eind voldoende omvangrijk werk geleverd. Gegeven een gemiddelde typesnelheid van 50 woorden per minuut, ben je dus 0,25 % van je tijd bezig met je proefschrift. Dat geeft lekker veel tijd voor het onderzoek zelf.

Ik weet nog goed dat ik tegen het eind van mijn afstuderen uit het raam staarde en dacht: "Het zit er bijna op, hier op de universiteit ..." Het treurige gevoel dat opkwam, gaf aan dat de omgeving, het onderwerp en het onderzoek leuk genoeg zijn om er nog een tijdje aan vast te knopen. Ik vind het leuk om met de techniek bezig te zijn en als aio krijg je ruim de tijd om ergens lekker diep in te duiken. En het schrijven van papers en een proefschrift? Ach, het draait toch om de inhoud, dus dat zal wel loslopen ... Ik ben mijn opa en Jan dankbaar voor de stimulans om eraan te beginnen. Daarnaast heeft Gerard een goede plek geboden, zodat ik kon uitpluizen wat ik leuk vind.

Zoals iedere aio wel weet, kost schrijven toch iets meer tijd dan die 0,25 %. Echter, de scheidslijn tussen onderzoek doen en schrijven is heel dun; door de ideeën op papier uit te werken, krijgen ze vorm en worden ze scherper. En Marco, die al vroeg in het traject als begeleider betrokken raakte, heeft hier een zeer waardevolle bijdrage aan geleverd met zijn kennis, kritiek en uitdagingen.

Hoewel uiteindelijk alleen mijn naam op dit proefschrift staat, zijn er veel mensen die direct of indirect invloed hebben gehad op dit resultaat. In willekeurige volgorde bedank ik enkelen van deze: mijn kamergenoten Marco, Arjan, Robert en Koen voor de nodige discussies, overdenkingen en afleiding tijdens die stressvolle proefschriftschrijfdagen; Berend die zich moedig durfde te wagen in de donkere hoekjes¹ van Starburst; Bert, die het weer moest ontgelden wanneer er een (NFS-)server haperde, ook al kon hij daar niets aan doen; Marlous, Thelma en Nicole voor de ondersteuning bij allerlei praktische zaken, zoals het boeken van snoepreisjes naar conferenties; Pascal en Philip voor de geboden doorgroeimogelijkheden en een basis van een Latex-template voor dit proefschrift, die via een ingewikkelde reeks van afgeleiden door (onder anderen?) Albert, Vincent, Maurice en Timon bij mij is gekomen, waar ook ik vervolgens hier en daar een packagegenaan heb geknutseld; Hermen, die het is gelukd om de allerlaatste typefout uit m'n proefschrift te halen; Christiaan, Mark en alle anderen van CAES voor de pauzes en borrels, die altijd weer met een hoop lol en onzin werden gevuld.

<sup>&</sup>lt;sup>1</sup>Ho eens even, zoveel van die hoekjes zijn er helemaal niet!

De vier jaar (plus een beetje) zijn omgevlogen. Ik heb genoten van wat ik heb gezien, geleerd en gedaan. Mijn ouders hebben mij altijd gesteund en hebben meegeleefd tijdens verre reizen, waar ik ze erg dankbaar voor ben, maar ze kunnen het toch maar lastig volgen wat ik nu precies allemaal heb gedaan, ondanks mijn verwoede pogingen om het uit te leggen. Wellicht dat dit proefschrift helderheid biedt, want eindelijk staat het nu eens allemaal netjes bij elkaar ...

Voor de laatste loodjes krijg ik hulp van mijn paranimfen, mijn beste vriend en geregelde lunchwandelgenoot Martijn, en aanstaande schoonvader Henk. Tot slot, ik ben heel blij met mijn geliefde, Marjan, die het altijd weer lukt om me op te vrolijken, wanneer er bijvoorbeeld een paper werd afgewezen, en die ik vaker dan eens heb beloofd om nu eens eerder thuis te komen, zodat we om een fatsoenlijke tijd kunnen eten.

Jochem Enschede, april 2014

# **CONTENTS**

| 1 | Int | RODUCTION                                                                             | 1                    |

|---|-----|---------------------------------------------------------------------------------------|----------------------|

|   | 1.1 | Multicore and many-core                                                               | 3                    |

|   | 1.2 | Abstraction                                                                           | 4                    |

|   | 1.3 | Embedded systems                                                                      | 6                    |

|   | 1.4 | Problem statement and approach                                                        | 6                    |

|   | 1.5 | Contributions                                                                         | 7                    |

|   | 1.6 | Structure                                                                             | 8                    |

|   |     |                                                                                       |                      |

| 2 | Tre | ands in Many-Core Architectures                                                       | 11                   |

|   | 2.1 | Ten many-core architectures                                                           | 11                   |

|   | 2.2 | Simpler cores, more performance                                                       | 12                   |

|   | 2.3 | Transparent processing tiles                                                          | 14                   |

|   | 2.4 | Interconnect: coherency traffic vs. data packets                                      | 15                   |

|   | 2.5 | Weak-memory hierarchy                                                                 | 16                   |

|   | 2.6 | Programming model consensus                                                           | 18                   |

|   | 2.7 | Starburst . 2.7.1 System overview . 2.7.2 OS: Helix . 2.7.3 Application environment . | 19<br>19<br>20<br>22 |

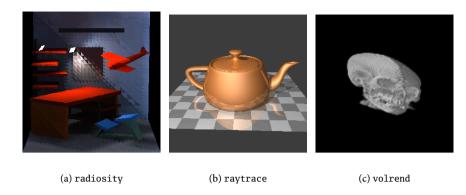

|   | 2.8 | Benchmark applications 2.8.1 SPLASH-2 2.8.2 PARSEC 2.8.3 NoFib                        | 22<br>23<br>24<br>25 |

|   |     | 2.0.3 INUTIO                                                                          | 25                   |

| 3 | PLA | TFORMS AND PROGRAMMING ABSTRACTION                                                                                                                                                            | 27                         |

|---|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

|   | 3.1 | Many-core hardware is the driving force                                                                                                                                                       | 28                         |

|   | 3.2 | Memory model—the hardware's contract                                                                                                                                                          | 29                         |

|   | 3.3 | A concurrency model to orchestrate interaction                                                                                                                                                | 31                         |

|   | 3.4 | Computation and algorithms                                                                                                                                                                    | 33                         |

|   | 3.5 | Programming model: a peephole view 3.5.1 Existing programming language's models 3.5.2 Less is more                                                                                            | 35<br>35<br>38             |

|   | 3.6 | Platform and portability                                                                                                                                                                      | 39                         |

|   | 3.7 | Related work                                                                                                                                                                                  | 41                         |

|   | 3.8 | Conclusion                                                                                                                                                                                    | 42                         |

| 4 | Eff | icient Hardware Infrastructure                                                                                                                                                                | 45                         |

|   | 4.1 | Communication patterns and topology                                                                                                                                                           | 47                         |

|   | 4.2 | Baseline: Starburst with Æthereal 4.2.1 8-core setup 4.2.2 Synthesis results: exponential costs 4.2.3 Core utilization by benchmark applications 4.2.4 Shortcomings of connection orientation | 48<br>48<br>50<br>51<br>52 |

|   | 4.3 | Warpfield: a connectionless NoC                                                                                                                                                               | 53<br>53<br>56<br>57       |

|   | 4.4 | Inter-core synchronization profile 4.4.1 Polling main memory measurements 4.4.2 Mutex locality                                                                                                | 60<br>61<br>63             |

|   | 4.5 | Asymmetric distributed lock algorithm 4.5.1 Existing synchronization solutions 4.5.2 The algorithm: a three-party asymmetry 4.5.3 Experimental comparison results 4.5.4 Locality trade-off    | 64<br>64<br>65<br>68<br>70 |

|   | 4.6 | Hardware and performance scalability                                                                                                                                                          | 72                         |

|   | 4.7 | Conclusion                                                                                                                                                                                    | 74                         |

| 5 | Usable Weak Memory Model                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                   |  |  |

|---|-----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|--|--|

|   | 5.1                                                                   | The problem with memories                                                                                                                                                                                                                                                                                                                                                                                                                                               | 78                                                                                |  |  |

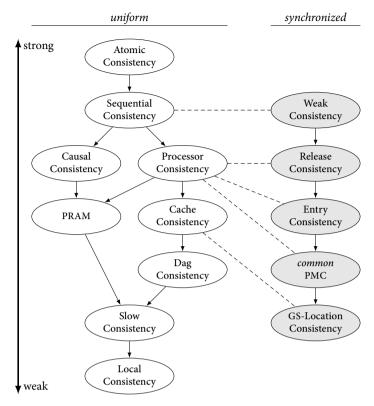

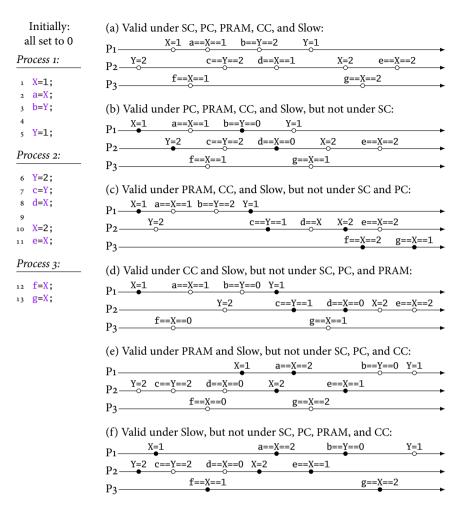

|   |                                                                       | 5.1.1 Various memory models                                                                                                                                                                                                                                                                                                                                                                                                                                             | 79                                                                                |  |  |

|   |                                                                       | 5.1.2 PMC's basic idea                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 84                                                                                |  |  |

|   | 5.2                                                                   | A Portable Memory Consistency model                                                                                                                                                                                                                                                                                                                                                                                                                                     | 86                                                                                |  |  |

|   |                                                                       | 5.2.1 Fundamentals                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 86                                                                                |  |  |

|   |                                                                       | 5.2.2 Operations by processes                                                                                                                                                                                                                                                                                                                                                                                                                                           | 87                                                                                |  |  |

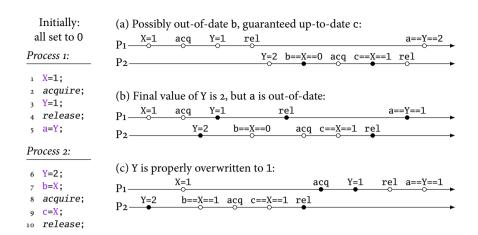

|   |                                                                       | 5.2.3 Orderings: semantics of operations                                                                                                                                                                                                                                                                                                                                                                                                                                | 88                                                                                |  |  |

|   |                                                                       | 5.2.4 Observing slowly                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 91                                                                                |  |  |

|   |                                                                       | 5.2.5 Comparison to existing models                                                                                                                                                                                                                                                                                                                                                                                                                                     | 92                                                                                |  |  |

|   | 5.3                                                                   | Annotation and abstraction                                                                                                                                                                                                                                                                                                                                                                                                                                              | 93                                                                                |  |  |

|   |                                                                       | 5.3.1 Front-end: annotations in source code                                                                                                                                                                                                                                                                                                                                                                                                                             | 93                                                                                |  |  |

|   |                                                                       | 5.3.2 Back-end example: three views on Starburst                                                                                                                                                                                                                                                                                                                                                                                                                        | 95                                                                                |  |  |

|   | 5.4                                                                   | Case study                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 100                                                                               |  |  |

|   |                                                                       | 5.4.1 Software cache coherency: SPLASH-2 benchmark                                                                                                                                                                                                                                                                                                                                                                                                                      | 100                                                                               |  |  |

|   |                                                                       | 5.4.2 Distributed shared memory: multi-reader/-writer FIFO                                                                                                                                                                                                                                                                                                                                                                                                              | 102                                                                               |  |  |

|   |                                                                       | 5.4.3 Scratchpad memory: motion estimation                                                                                                                                                                                                                                                                                                                                                                                                                              | 103                                                                               |  |  |

|   | 5.5                                                                   | Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 105                                                                               |  |  |

|   |                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                   |  |  |

|   |                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                   |  |  |

| 6 | Імр                                                                   | LICIT SOFTWARE CONCURRENCY                                                                                                                                                                                                                                                                                                                                                                                                                                              | 109                                                                               |  |  |

| 6 | IMP<br>6.1                                                            | Basic idea                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 109<br>111                                                                        |  |  |

| 6 |                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | _                                                                                 |  |  |

| 6 | 6.1                                                                   | Basic idea                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 111                                                                               |  |  |

| 6 | 6.1<br>6.2                                                            | Basic idea                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 111<br>112                                                                        |  |  |

| 6 | 6.1<br>6.2                                                            | Basic idea                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 111<br>112<br>113                                                                 |  |  |

| 6 | 6.1<br>6.2                                                            | Basic idea                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 111<br>112<br>113<br>113                                                          |  |  |

| 6 | 6.1<br>6.2                                                            | Basic idea  Related work  Shift in paradigm: $\lambda$ -calculus and its implementation  6.3.1 Background on $\lambda$ -calculus  6.3.2 Our simple functional language: LambdaC++  6.3.3 The atomic-free core: data races and lossy work queue                                                                                                                                                                                                                          | 111<br>112<br>113<br>113<br>115                                                   |  |  |

| 6 | 6.1<br>6.2<br>6.3                                                     | Basic idea  Related work  Shift in paradigm: $\lambda$ -calculus and its implementation  6.3.1 Background on $\lambda$ -calculus  6.3.2 Our simple functional language: LambdaC++                                                                                                                                                                                                                                                                                       | 111<br>112<br>113<br>113<br>115<br>124                                            |  |  |

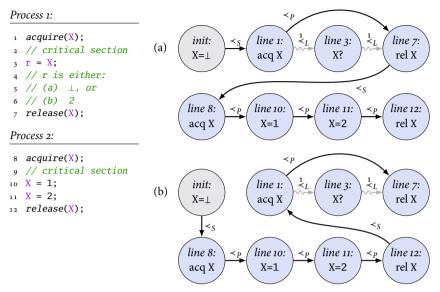

| 6 | 6.1<br>6.2<br>6.3                                                     | Basic idea  Related work  Shift in paradigm: $\lambda$ -calculus and its implementation  6.3.1 Background on $\lambda$ -calculus  6.3.2 Our simple functional language: LambdaC++  6.3.3 The atomic-free core: data races and lossy work queue  Impact on memory consistency and synchronization                                                                                                                                                                        | 111<br>112<br>113<br>113<br>115<br>124<br>126                                     |  |  |

| 6 | <ul><li>6.1</li><li>6.2</li><li>6.3</li></ul>                         | Basic idea  Related work  Shift in paradigm: $\lambda$ -calculus and its implementation  6.3.1 Background on $\lambda$ -calculus  6.3.2 Our simple functional language: LambdaC++  6.3.3 The atomic-free core: data races and lossy work queue  Impact on memory consistency and synchronization  6.4.1 A $\lambda$ -term's life and rules  6.4.2 Mapping from rules to PMC                                                                                             | 111<br>112<br>113<br>113<br>115<br>124<br>126<br>126                              |  |  |

| 6 | 6.1<br>6.2<br>6.3                                                     | Basic idea  Related work  Shift in paradigm: $\lambda$ -calculus and its implementation  6.3.1 Background on $\lambda$ -calculus  6.3.2 Our simple functional language: LambdaC++  6.3.3 The atomic-free core: data races and lossy work queue  Impact on memory consistency and synchronization  6.4.1 A $\lambda$ -term's life and rules  6.4.2 Mapping from rules to PMC  Experiments                                                                                | 111<br>112<br>113<br>113<br>115<br>124<br>126<br>128<br>132                       |  |  |

| 6 | <ul><li>6.1</li><li>6.2</li><li>6.3</li></ul>                         | Basic idea  Related work  Shift in paradigm: $\lambda$ -calculus and its implementation  6.3.1 Background on $\lambda$ -calculus  6.3.2 Our simple functional language: LambdaC++  6.3.3 The atomic-free core: data races and lossy work queue  Impact on memory consistency and synchronization  6.4.1 A $\lambda$ -term's life and rules  6.4.2 Mapping from rules to PMC  Experiments                                                                                | 111<br>112<br>113<br>113<br>115<br>124<br>126<br>126                              |  |  |

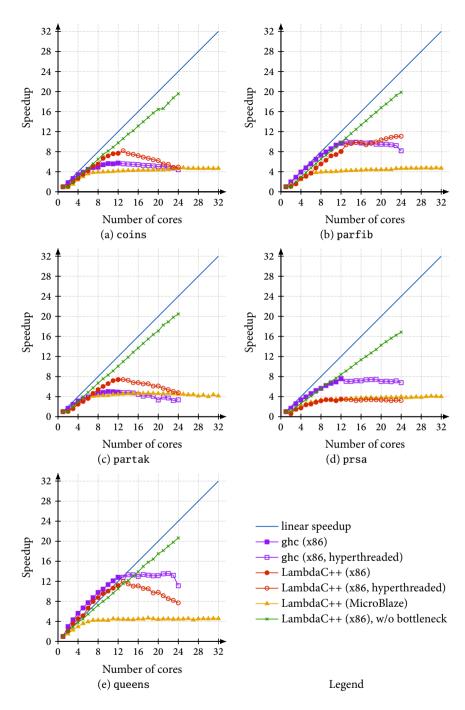

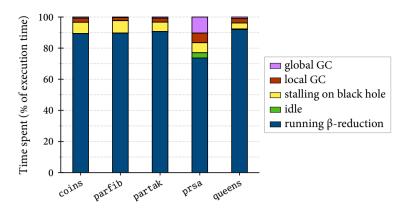

| 6 | <ul><li>6.1</li><li>6.2</li><li>6.3</li><li>6.4</li><li>6.5</li></ul> | Basic idea  Related work  Shift in paradigm: $\lambda$ -calculus and its implementation  6.3.1 Background on $\lambda$ -calculus  6.3.2 Our simple functional language: LambdaC++  6.3.3 The atomic-free core: data races and lossy work queue  Impact on memory consistency and synchronization  6.4.1 A $\lambda$ -term's life and rules  6.4.2 Mapping from rules to PMC  Experiments  6.5.1 Scalability and speedup                                                 | 111<br>112<br>113<br>113<br>115<br>124<br>126<br>128<br>132                       |  |  |

| 6 | <ul><li>6.1</li><li>6.2</li><li>6.3</li><li>6.4</li><li>6.5</li></ul> | Basic idea  Related work  Shift in paradigm: $\lambda$ -calculus and its implementation $6.3.1$ Background on $\lambda$ -calculus $6.3.2$ Our simple functional language: LambdaC++ $6.3.3$ The atomic-free core: data races and lossy work queue  Impact on memory consistency and synchronization $6.4.1$ A $\lambda$ -term's life and rules $6.4.2$ Mapping from rules to PMC  Experiments $6.5.1$ Scalability and speedup $6.5.2$ Locality and overhead             | 111<br>112<br>113<br>113<br>115<br>124<br>126<br>128<br>132<br>132<br>135         |  |  |

| 7 | <ul><li>6.1</li><li>6.2</li><li>6.3</li><li>6.4</li><li>6.5</li></ul> | Basic idea  Related work  Shift in paradigm: $\lambda$ -calculus and its implementation $6.3.1$ Background on $\lambda$ -calculus $6.3.2$ Our simple functional language: LambdaC++ $6.3.3$ The atomic-free core: data races and lossy work queue  Impact on memory consistency and synchronization $6.4.1$ A $\lambda$ -term's life and rules $6.4.2$ Mapping from rules to PMC  Experiments $6.5.1$ Scalability and speedup $6.5.2$ Locality and overhead             | 111<br>112<br>113<br>113<br>115<br>124<br>126<br>128<br>132<br>132<br>135         |  |  |

|   | <ul><li>6.1</li><li>6.2</li><li>6.3</li><li>6.4</li><li>6.5</li></ul> | Basic idea  Related work  Shift in paradigm: $\lambda$ -calculus and its implementation $6.3.1$ Background on $\lambda$ -calculus $6.3.2$ Our simple functional language: LambdaC++ $6.3.3$ The atomic-free core: data races and lossy work queue  Impact on memory consistency and synchronization $6.4.1$ A $\lambda$ -term's life and rules $6.4.2$ Mapping from rules to PMC  Experiments $6.5.1$ Scalability and speedup $6.5.2$ Locality and overhead  Conclusion | 1111<br>112<br>113<br>113<br>115<br>124<br>126<br>128<br>132<br>132<br>135<br>136 |  |  |

| $\circ$        |  |

|----------------|--|

| 0              |  |

| Z              |  |

| Η              |  |

| Ξ              |  |

| 4              |  |

| $\overline{z}$ |  |

|                |  |

| A   | ETY    | MOLOGY       | 147 |

|-----|--------|--------------|-----|

|     | A.1    | Starburst    | 147 |

|     | A.2    | Warpfield    | 147 |

|     | A.3    | Helix        | 148 |

|     | A.4    | skat         | 148 |

|     | A.5    | LambdaC++    | 149 |

| Ac  | RONY   | MS           | 153 |

| Вів | LIOG   | RAPHY        | 157 |

| Lis | T OF ] | Publications | 169 |

| Ind | EX     |              | 171 |

# Introduction

ABSTRACT – Processors incorporate more and more cores. With the increasing core count, it becomes harder to implement convenient features like atomic operations, ordering of all memory operations, and hardware cache coherency. When these features are not supported by the hardware, applications become more complex. This makes programming these many-core architectures hard. This thesis defines programming models for many-core architectures, such that current trends in processor design can be dealt with. Finding a good balance between choices regarding different layers of the platform is essential in order to ease programming. Throughout the thesis, design choices and consequences are evaluated based on a co-design of hardware and software abstraction layers.

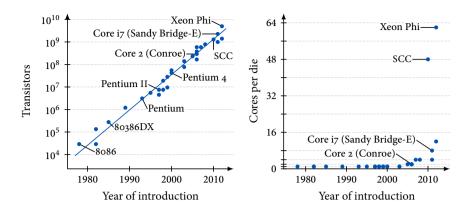

"The single-core era has ended, multicore processors are here to stay. Getting 'free' computing power by just increasing the clock frequency, does not work anymore. So, when one processor does not get faster, just use multiple of them." This has been said many times, and it is illustrated in figure 1.1 on the following page. In 2005, both Intel and AMD introduced a multicore processor, which marks an important transition. In the past, parallelism was only achieved by putting multiple processors together for specific systems like servers and supercomputers. Now, processors make every (consumer) system a parallel machine. Programmers accept the fact that they have to face programming for concurrency. Although it might sound like a reasonable conclusion, 'just' having multiple cores only adds *raw* computing power, but does not imply that software can make use of it.

Software for a single-core system behaves in a way programmers can understand easily. Instructions are executed in the order that is defined, and if designed carefully, the program always gives a correct result. When the computer becomes faster, e.g., runs at a higher clock speed, the software will run faster. Many (single-core) technological enhancements, like smaller feature sizes, caches, and branch prediction, can be applied to the processor architecture and improve performance without changes to the software.

FIGURE 1.1 – Various Intel microprocessors

In great contrast, exploiting hardware parallelism (in the form of multiple cores) by concurrent programming can only be accomplished when the software is changed. The program has to be split in chunks of work that can be executed in parallel. Based on the single-core programming principles, programming involves defining a somewhat balanced set of communicating instruction sequences. When a multicore computer becomes faster—which effectively means that more cores are added—a properly balanced multi-threaded program might not even benefit at all. More importantly, when the speed of a hardware component changes, the latency and interleaving of communication might change too and even break the program. Such bugs are hard to find, even harder to reproduce, and therefore almost impossible to fix properly. Moving from single-core to multicore is one example of an improvement to a computer system as a whole, which requires changes to multiple aspects of the design of such a system; this truly requires *co-design* of the hardware architecture and the programming approach.

Hardware and software have influenced each other for a long time. An example of the hardware–software interplay is the addition of threading to the latest C and C++ standards, as a response to multicore hardware. The introduction of vector instructions in general-purpose processors as a response to the increasing demand for graphics processing, is just another example. So, co-design is commonly applied in processor design.

Nevertheless, several trends are visible that pushes hardware complexity via the programming model to the application. Borkar and Chien [22] conclude that the performance of hardware can only be increased under acceptable energy demands, when software supports these changes to the hardware. While hardware can only respond to events that occur at this moment, software has some knowledge and control over the future, e.g., by scheduling. Therefore, software might be able to reduce

the power usage more than hardware can do, by taking control over fine-grained dynamic power management, such as turning off cores that are not to be used soon. A different trend shows that the performance of memory technology scales not as fast as the performance of logic circuitry, so memory becomes a bottleneck, and the software should exploit data locality even more. Therefore, the memory hierarchy becomes more complex, e.g., because of multiple levels of caches, and control over this hierarchy lies in the hands of software [29]. Another trend can be seen in how concurrency is handled. More parallelism can only be realized by a change in the programming paradigm [105]. However, it is hard to accomplish this. Threading is a popular approach, but it introduces non-determinism at such a scale, that it is hard to oversee and control by a programmer [71]. Additionally, threading libraries might break optimizations by a concurrency-agnostic compiler [20]. Among many other APIs, OpenMP [36] allows fine-grained control over parallelism, which a compiler cannot statically determine by itself, by means of annotations in the C source code. In all these trends, handling of low-level machine-specific details is based on analysis of, or control by, the high-level (pseudo-)machine-independent application. In practice, however, the programmer has to do it by hand...

It is logical to expose new hardware features to the programmer first, and rely on manual control; it takes time until the feature is understood well enough to take care of it automatically. However, the ultimate goal is to let a tool do all the work that can be done automatically. In case of the aforementioned multicore trends, parallelism and the memory hierarchy are features that are hard to handle correctly by hand. The question is whether it can be automated or not, and what the consequences are. This thesis will discuss consequences of choices regarding various abstraction layers that are relevant for programming a multicore system.

#### 1.1 MULTICORE AND MANY-CORE

Let us first define such a 'multicore' system in the context of this thesis. A parallel machine can be organized in many ways, such as: multiple cores within a processor, communicating via an on-chip bus; multiple processors within a computer, communicating via an off-chip bus; and multiple computers within a cluster, communicating via Ethernet. These architectures all have their benefits and drawbacks.

One interesting property is the latency of communication. As an example, different latencies of reads within the Intel Nehalem processor are listed in table 1.1 on the next page [81]. It shows that off-chip communication takes a considerable amount of time, compared to reads from memories that are closer. Combined with the trend of figure 1.1, the continuing exponential growth of the number of transistors per chip gives resources and a performance benefit to integrate more cores on one die. Hence, it is likely that the number of cores per processor will grow exponentially.

Multicore systems are often classified as *many-core* to express a high core count. It also informally tends to stress the need for specific techniques that are related to

| latency (cycles) |

|------------------|

| 4                |

| 10               |

| 38               |

| 38-83            |

| 102-170          |

| 191              |

| 310              |

|                  |

TABLE 1.1 - Read latency (Intel Nehalem) [81]

concurrency. However, the exact difference between multi and many is usually not clearly defined. We use the following definition:

#### multicore

A symmetric multiprocessing (SMP) architecture containing tightly coupled identical superscalar cores, under control of a single OS. The cores are tightly coupled in the sense that they (usually) share all memory, and the caches are hardware cache coherent.

#### many-core

A processor architecture that contains at least tens of loosely coupled (possibly heterogeneous) simpler cores. The cores are loosely coupled in the sense that the memory is characterized as a non-uniform memory architecture (NUMA), they (usually) have incoherent caches, and every core runs its own (instance of an) OS.

Most commercially available processors can be described as multicores. The Intel SCC and Intel Xeon Phi can be classified as many-cores, even though the latter has hardware cache coherency. As the core count increases, hardware cache coherency is unlikely to sustain [29], which will probably make most future processors many-cores.

This thesis focuses on programming a single many-core processor. From a software perspective, this conceptually does not differ much from a multiprocessor setup. Therefore, we use the terms 'core' and 'processor' as synonyms, despite their physical differences.

#### 1.2 Abstraction

Making abstractions, as we just did, is very important in programming. A computer consists of many abstraction layers, which hide details about the implementation. Table 1.2 lists several layers of abstraction within a processor. All these layers are replaceable, without having to redefine all other layers, except for the surrounding onces. For example, when CMOS technology is replaced, the standard cells have to be redesigned, but the processor architecture is (largely) independent of it.

TABLE 1.2 - Abstraction layers

| model                              | examples                |

|------------------------------------|-------------------------|

| programming language               | C, Haskell              |

| •••                                |                         |

| logical processors                 | context switching by OS |

| instruction set                    | x86-64, Thumb-2         |

| processor                          | Phenom II, MicroBlaze   |

| core                               | IA-32, hyperthreading   |

| components                         | RAM, ALU                |

| standard cells                     | and-gate, flip-flop     |

| circuit logic                      | CMOS                    |

| semiconductor                      | GaAs                    |

| atoms                              | Si, O                   |

| Standard Model of particle physics | up quark, muon neutrino |

An abstraction generalizes the implementation of it. As such, conclusions drawn, based on the abstraction, should be valid for every implementation. In the examples of table 1.2, two different types of abstraction can be observed: the abstraction contains either *fewer* or *more* details than its implementation. The abstraction of CMOS technology to standard cells hides all details about feature size and thickness of the metal layers. Such an abstraction layer has to fill in the missing details, which usually comes at a cost or overhead—rectangular shaped standard cells do not necessarily use the least amount of chip area. In contrast, the x86-64 is a CISC instruction set, where processors translate it to a RISC set of simpler micro-operations. So, CISC instructions carry more information than what is required by the processor; the implementation of the abstraction layer can make optimal choices, based on the abundant information.

The programming language at the top of the list does not fit in this definition of an abstraction. It partly hides details, such as details of the assembly language of the specific target processor. However, it exposes issues like concurrency and interthread communication. For example in C, concurrency is something that has to be done by the programmer. Most importantly, different programming languages hide and expose different aspects. For portability reasons, a proper programming model is required.

The (software-related) abstraction layers at the top of table 1.2 are not as clearly delimited as those at the bottom. The question is whether proper layers can be defined, and in what way implementation details can be hidden from the programmer. In this thesis, we discuss the abstraction layers that are relevant from a programming perspective, and how these abstractions influence each other. A good programming model is designed such that it allows utilizing the raw computing power of a many-core architecture, with a high level of abstraction.

#### 1.3 EMBEDDED SYSTEMS

If utilizing all computer power, i.e. performance, is not relevant, programming a multicore system is rather straightforward; use one core, and leave all the others idle. For a desktop PC, this might be acceptable in some cases. However, within the embedded domain, resources are more precious or performance requirements stricter. Embedded system processors follow the same trends as figure 1.1 on page 2 illustrates for desktop and server systems. The same technology is used, but there is a time offset of several years in which the technology becomes mature, more energy efficient, and feasible to be used in battery-powered devices. For example, where the first iPhone in 2007 uses a single-core ARM processor, the first quad-core smartphones appeared in 2012.

Moreover, embedded systems are often used in a context where time-critical interaction with the environment is required. Examples include video decoding with a constant frame rate, and control of a car or airplane. In this sense, embedded systems are pushed to their limits, which makes investments in new techniques worthwhile, which in turn can also be applied in general-purpose computing at a later stage. The combination of limited resources and performance requirements in an embedded system makes the multicore programming challenge even more interesting. The techniques presented in this thesis are therefore tailored towards embedded systems, but might also be applicable in other systems.

#### 1.4 PROBLEM STATEMENT AND APPROACH

As discussed above, processors become increasingly parallel. In an embedded context, it is important to maximize the performance and therefore to utilize all available cores. However, in many-core architectures, concessions to programmability are made by changing several aspects of the architecture in favor of hardware scalability, production costs, reduced design complexity, or energy efficiency. These changes to the hardware are reflected in the programming model, and are currently exposed to the programmer. The central problem this thesis addresses is:

How can we cope with the hardware trends in embedded many-core architectures, from a programming perspective?

The approach is to define *programming models* in a way that the complexity of the trends mentioned above is hidden from the programmer. Then, the compiler and a run-time system should have all information to handle low-level details automatically, efficiently, and correctly. We limit ourselves to the following aspects.

At the hardware-architectural level, a network-on-chip (*NoC*) with a mesh topology is often advocated as a scalable interconnection infrastructure. However, such an interconnect requires routing through the mesh. To guarantee bandwidth between two cores or to memory, the communication pattern of the application is required to determine the allocation of buffers and network links. Such a communication

pattern is assumed to be pseudo-static—it is static during a specific phase of the program, but changes over the phases. However, the preferred programming approach, C and threads, does not match the requirement that the communication pattern has to be known on beforehand. Additionally, as the latency in number of clock cycles increases at an increasing core count, atomic operations like a compare-and-swap are hard to realize. When these operations are absent or more expensive, it influences the choices a programmer might make about concurrency. We investigate the *interconnect*, guarantees about inter-core communication, and *synchronization* protocols, and we propose a new interconnect that better suits the needs.

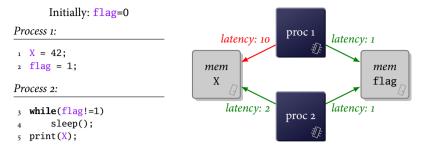

As a NUMA architecture is used, e.g., by using scratchpad memories, the performance is influenced by the location where application data is stored. Moreover, as processors and memories are distributed, a total ordering of operations on them cannot be guaranteed. This makes it harder to reason about the behavior of the memory and therefore the system state. Additionally, hardware cache coherency becomes notoriously complex at high core counts, but incoherent caches make the memory behavior even harder to understand. We define a *memory model* that is able to hide handling caches and scratchpad memories, and allows easily porting applications to other memory architectures.

The actual number of cores is usually not known at compile time. Therefore, the application has to be suitable to be run on any number of cores. This has a major impact on how an application should be designed and written. Defining *concurrency* in an application by hand is error-prone. We discuss a scalable programming approach to do this automatically.

Every layer of abstraction has influence on the surrounding layers. More importantly, choices regarding a lower level have an impact on programming. Therefore, we evaluate all decisions in a *co-design* approach, such that the overall programming efficiency is improved.

#### 1.5 Contributions

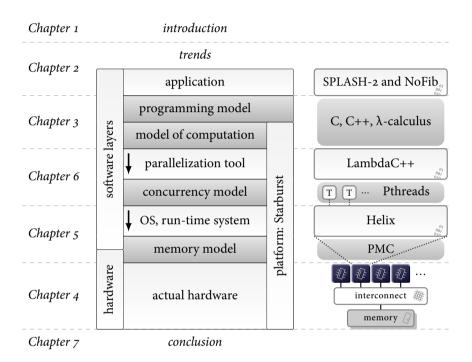

The central concept of this thesis is the definition of a programming model with respect to the hardware–software platform. A platform contains a hardware architecture, and implements a memory model and a concurrency model. On top of that, a model of computation is combined with a programming paradigm in a programming model. The programming model exposes specific details of the underlying models, but hides others. We define a layered overview of a programming model, which allows characterization of programming languages, based on what information a programming should give to guide a proper implementation.

We propose a tree-shaped interconnect with a ring for core-to-memory and core-to-core communication, respectively. The interconnect uses a work-conserving distributed first-come-first-served arbitration scheme, and gives bandwidth guarantees. The hardware costs are low and scale linearly to the number of cores.

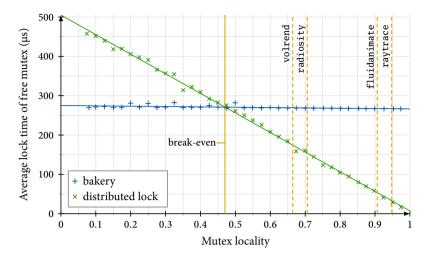

As atomic read–modify–write operations are hard to realize in a many-core architecture, synchronization is usually based on polling background memory, which is expensive in terms of bandwidth. We present a distributed lock algorithm, which benefits from the local memories and bypasses the background memory.

Cache coherency, scratchpad memories, and distributed shared memory are generalized in our proposed Portable Memory Consistency (*PMC*) model. This model allows abstracting from any memory architecture, while retaining the essential memory operation orderings that are required for programming. We show an implementation to several memory architectures, including software cache coherency, which is transparently applied to standard benchmark applications.

Finally, we present an implementation of a functional language, which utilizes the full parallel capacity of a many-core system. Most interestingly, the implementation is *atomic-free*; no locks, atomic read–modify–write operations, or strong memory model is required. This property allows a further increase of the number of cores, while locality can be exploited transparently.

All experiments are conducted on Starburst, our many-core system on FPGA, using standard benchmark applications. The system reflects the current trends in many-core architectures. This allows evaluation of all aforementioned aspects in a realistic environment.

#### 1.6 STRUCTURE

This thesis is organized as depicted by the figure on page 10. The layered view of a many-core platform with the programming model form the core of the thesis.

Chapter 2 discusses trends in many-core architectures and applications. Based on the observed trends, we designed and implemented our experimental platform Starburst. The parallel benchmarks applications from the SPLASH-2 and NoFib are discussed, which we use throughout the thesis for evaluation.

In chapter 3, all layers in the figure are discussed in more detail. The programming model is defined, in terms of the underlying models. To make programming easier, the programming model should hide as many details from the other layers as possible. To this extent, specific optimizations in the remaining layers are discussed in chapters 4 to 6 in a bottom-up fashion.

Chapter 4 discusses the communication infrastructure and synchronization. The tree-shaped interconnect is presented, in combination with core-to-core communication that is required for the distributed lock algorithm. Chapter 5 presents the PMC model and an approach to annotate existing applications in order to be portable to any memory architecture. Chapter 6 presents a method that hides concurrency from the programmer, but still allows utilizing all cores.

Finally, chapter 7 concludes the thesis, formulates the contributions in more detail, and presents recommendations for future work.

This empty page leaves some room for random thoughts:

The universe is inherently parallel, and laws of nature are applied everywhere without computational effort and error margin. Why is it that hard for a computer in the same universe to do a universe-compatible N-body simulation?

Thesis overview

# TRENDS IN MANY-CORE ARCHITECTURES

ABSTRACT – Based on a comparison of ten contemporary commercial many-core architectures, several trends can be observed. The cores are relatively simple, and memory bandwidth per core is limited. Most architectures have multi-level caches, which are hardware cache coherent. However, weak memory models are used. In contrast to the attention in research, only a few architectures have scratchpad memories. Our many-core architecture, Starburst, captures both commercial and research trends.

Chapter 1 discussed the trends of microprocessors, and concluded that every processor will become a multicore one. The tendency is that locality is crucial for performance. In this chapter, we discuss several commercial processors in more detail, and relate these to the high-level trends above. For evaluation purposes throughout the thesis, we designed and built the many-core system Starburst, which reflects these trends in current and expected future architectures.

#### 2.1 TEN MANY-CORE ARCHITECTURES

Table 2.1 on the following page lists several multicore architectures of the last several years. These architectures all are single chip packages, deliver a high performance by utilizing multiple cores, and are commercially available, except for the experimental Intel SCC. All architectures are targeting high-performance computing, except for the Adapteva Epiphany-IV and Samsung Exynos 4 Quad. These two systems are designed for embedded systems with a limited power budget, like smartphones and tablets.

The table shows the number of cores and the total number of hardware-supported threads. All these cores are homogeneous. Although some systems include several

|                         | [ref.] | year | core type      | cores<br>(threads) | clock<br>(MHz) |

|-------------------------|--------|------|----------------|--------------------|----------------|

| Tilera TILE-Gx8072      | [107]  | 2009 | DSP            | 72                 | 1 000          |

| IBM POWER7              | [66]   | 2010 | C1             | 8 (32)             | 3 5 5 0        |

| Oracle UltraSPARC T3    | [96]   | 2010 | SPARC V9       | 16 (128)           | 1 649          |

| Intel SCC               | [58]   | 2010 | Pentium-100    | 48                 | 1 000          |

| Intel i7-3930K          | [6o]   | 2011 | Sandy Bridge-E | 6 (12)             | 3 200          |

| Cavium OCTEON II CN6880 | [27]   | 2011 | cnMIPS64 v2    | 32                 | 1 500          |

| Adapteva Epiphany-IV    | [3]    | 2011 | RISC           | 64                 | 800            |

| Samsung Exynos 4 Quad   | [118]  | 2012 | ARM Cortex-A9  | 4                  | 1400           |

| Freescale T4240         | [42]   | 2012 | Power e6500    | 12 (24)            | 1800           |

| Intel Xeon Phi          | [61]   | 2012 | x86-64, vector | 61 (244)           | 1 2 3 8        |

| Starburst               |        |      | MicroBlaze     | 32                 | 100            |

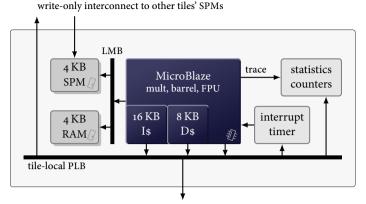

accelerators, these are not taken into account for the core count. As the number of transistors per chip increases, it is expected [22] that processors will integrate more heterogeneous cores or more accelerators, but this is not reflected in most of the systems listed—only the Cavium OCTEON II CN6880, Freescale T4240, and Exynos 4 Quad integrate accelerators for graphics or other applications. Starburst¹ (in the form it is discussed in this thesis) is a homogeneous MicroBlaze system with a configurable core count of up to 32. In contrast to all other architectures, it is mapped onto an FPGA, which limits the clock frequency to 100 MHz.

It is clear that contemporary high-end systems already require tens to hundreds of concurrent threads to utilize the full hardware of a single processor. We do not consider (general-purpose) GPUs at this point. Although these processors have thousands of cores, there usability is limited to parallel vector operations, like graphics and specific scientific workloads. Moreover, there are constraints in memory accesses, code and data size, etc. In general, all systems of table 2.1 are (supposed to be) programmed in C with threads, which cannot be done on a GPU.

The setup of these systems is very common: cores have a small L1 instruction and data cache. Often, cores are grouped in clusters of two or four cores, which connect via a low-latency interconnect to a shared L2 cache. Furthermore, the individual cores or clusters are connected via a NoC with a mesh topology or a multilayer bus to each other, and via one or more memory controllers to external DDR memory. The individual properties are discussed in more detail in the subsequent sections.

#### 2.2 SIMPLER CORES, MORE PERFORMANCE

Single-core processors use the increasing amount of transistors to implement complex microarchitectural features like out-of-order execution, exploiting instruction-

<sup>&</sup>lt;sup>1</sup>Refer to appendix A for a description where the name comes from.

TABLE 2.2 - Core and memory performance

|                    | CoreMark   | CoreMark | shared-memory bandwidth <sup>a</sup> |                       |                        |

|--------------------|------------|----------|--------------------------------------|-----------------------|------------------------|

|                    | score [34] | per MHz  | in total<br>(GB/s)                   | per core<br>(B/cycle) | per CoreMark<br>(MB/s) |

| Tilera TILE-Gx8072 | 230 196    | 230.19   | 53.6                                 | 0.80                  | 0.238                  |

| IBM POWER7         | 336 196    | 94.70    | 95.4                                 | 3.61                  | 0.291                  |

| UltraSPARC T3      | 87 054     | 52.79    | 23.8                                 | 1.94                  | 0.280                  |

| Intel SCC          | 102 240    | 102.24   | 21                                   | 0.44                  | 0.210                  |

| Intel i7-3930K     | 150 962    | 41.17    | 47.7                                 | 2.67                  | 0.323                  |

| OCTEON II CN6880   | 153 477    | 102.32   | 46.6                                 | 1.04                  | 0.311                  |

| Epiphany-IV        | 78 749     | 98.44    | 6.4                                  | 0.13                  | 0.083                  |

| Exynos 4 Quad      | 22 243     | 15.89    | 6.4                                  | 1.23                  | 0.295                  |

| Freescale T4240    | 187874     | 104.37   | 46.9                                 | 2.33                  | 0.256                  |

| Starburst          | 4 5 2 1    | 45.21    | 0.391                                | 0.13                  | 0.088                  |

<sup>&</sup>lt;sup>a</sup> Peak core–shared-memory bandwidth, based on the memory controller or the interface to the interconnect

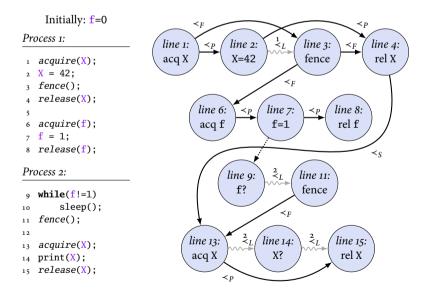

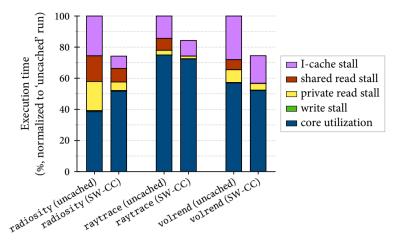

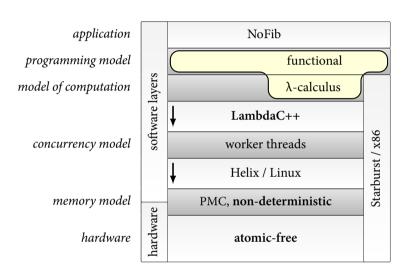

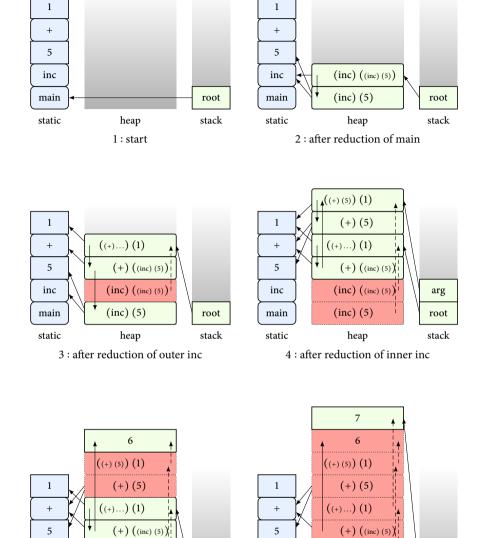

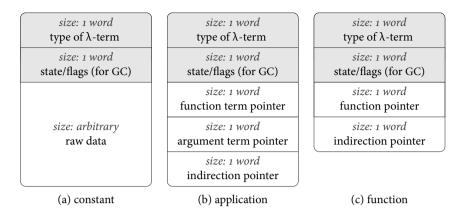

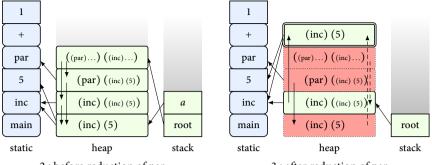

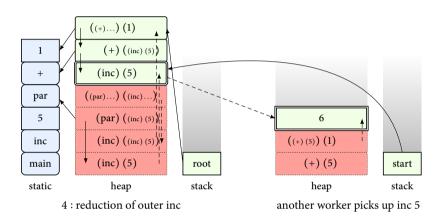

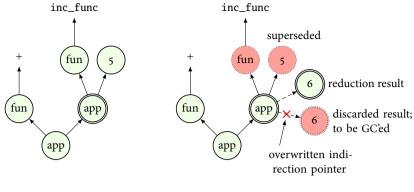

level parallelism (*ILP*), and deep pipelines. These features are relatively costly, compared to the gained speedup [22]. Once the burden to multicore and concurrency is overcome, it can be cost-effective to use simpler cores, but implement more of them. For example, Intel Xeon Phi's philosophy is to have many, but smaller cores than other Xeon processors. The UltraSPARC T<sub>3</sub> uses simpler in-order cores, but interleave instructions of many threads per core, such that the core's pipeline is filled, even when threads stall on cache misses, for example. Epiphany-IV and Exynos 4 Quad use RISC cores to reduce power usage. Interestingly, all systems either support SIMD instructions or have specific accelerators.